Как работают инструкции процессора?

В 32-битном процессоре, как я понимаю, каждая инструкция является 32-битной. Итак, для инструкции MOV в сборке, как вы используете только 32 бита для кода операции плюс параметры? Таким образом, для:

MOV register, [address]

Разве адрес не занимает 32 бита сам по себе? Так разве это не займет всю инструкцию?

Может быть, у меня все неправильно, но я пытаюсь реализовать виртуальную машину на C / C ++. Помогите?

Решение

Инструкции x86 имеют переменную длину. Процессор начинает чтение инструкции с первого байта, идентифицирует «код операции», затем продолжает чтение следующих байтов в зависимости от фактической инструкции.

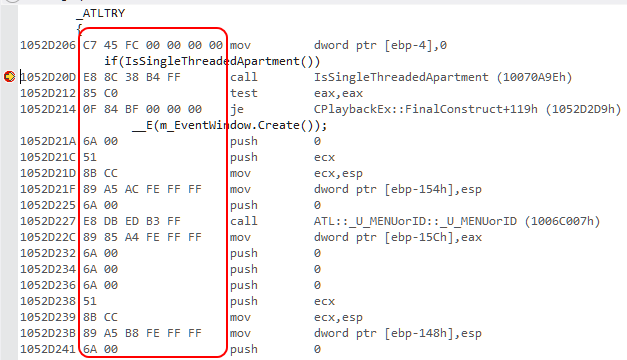

Я остановил отладчик (Visual Studio) в случайной точке, и в окне его разборки есть опция «Показать байты кода», которая дает пример длины инструкции. Посмотрите ниже:

В частности, посмотрите на строку с mov [ebp-15Ch], eax что близко к упомянутому в вашем вопросе. Соответствующие байты включают A4 FE FF FF который является 32-битным значением для -15Ch,

Другие решения

На самом деле, коды операций могут быть переменной длины или фиксированной длины в зависимости от архитектуры. Также есть 16- и 32-битные процессоры с 20-битной адресной шиной.

Ширина архитектуры не очень ясна в наши дни. Это больше историческая вещь. Я полагаю, что лучшим «определением» в наши дни может быть ширина «логической» внутренней базы данных.

(Вспомните 8088: 16-битное устройство с 8-битной мультиплексированной шиной данных.)

Некоторые процессоры, такие как x86, решают эту проблему с помощью инструкций переменной длины, поэтому инструкции не имеют длины 32 бита — в x86 есть некоторые инструкции длиной в один байт, а некоторые инструкции имеют длину более 10 байт. (Это также означает, что инструкции не всегда выровнены по 32-битным границам, очевидно).

Другие процессоры решают ее с помощью «постоянной части с двумя частями», например, ARM, MIPS и 29K имеют инструкции, которые загружают «нижнюю часть» и «верхнюю часть» как отдельные объекты (как правило, нижняя часть загрузки очищает или расширяет знак верхняя часть, а верхняя часть оставляет нижнюю часть неизменной, таким образом, небольшие значения могут быть загружены в одну инструкцию).

Конечно, в большинстве случаев мы имеем дело не с постоянными адресами, а с переменными, которые содержат адреса (так называемые указатели или ссылки), и в этом случае инструкция «load» загружается с адреса, который находится в регистре. , а не постоянное значение.

В ассемблере, таком как ARMv7, который является строго 32-битным, вы не можете хранить код операции и абсолютный адрес в одной инструкции. То, что вы должны сделать, это либо

- загрузить адрес из памяти в регистр, а затем перейти к адресу в регистре.

- сохранить адрес относительно счетчика программы [pc]

В этом может помочь руководство по архитектуре ARM.

Здесь есть хорошие ответы, объясняющие формат инструкции. Однако, похоже, никто не проясняет, что кажется вам путаницей: для 32-битной архитектуры инструкция операнды 32 бита (*), а не инструкции. Инструкция состоит из кода операции [и операндов] (не все инструкции имеют операнды, например, nop, sti).

(*) это не так не важно что править. Например, 32-битная архитектура x86 имеет расширение набора команд (SSE), которое принимает 128 и даже 256-битные операнды.

Процессоры Risk, такие как arm, имеют инструкции фиксированного размера. X86 — это процессор cisc (инструкции переменного размера). В случае процессора RISC 32-битный адрес делится на 2 части (16 бит — привет и младший) и загружается путем выполнения 2 инструкций загрузки в один регистр, а затем мы можем загрузить (переместить) содержимое адреса в другой регистр. Таким образом, может потребоваться до 3 инструкций для перемещения чего-либо в регистр из памяти.

Процессор не «общается» с ОС. Процессор — это просто схема. Схема декодирования команд активирует другие схемы на основе сопоставления с шаблоном с битами команд, которые она считывает из памяти.

Все они стандартизированы, поэтому одна ОС может работать на любом процессоре x86, например.

Однако 32-разрядный процессор будет обрабатывать меньше ресурсов, чем 64-разрядный процессор. Процессор можно разделить на блоки, а затем получить к ним доступ, как к микросхеме памяти.

Таким образом, все еще сложно написать программное обеспечение для вашего оборудования, если вас не поддерживает команда.